- Part Number Configuration Voltage Clock Rate / Access time Package Temperature SCD#

-

No record

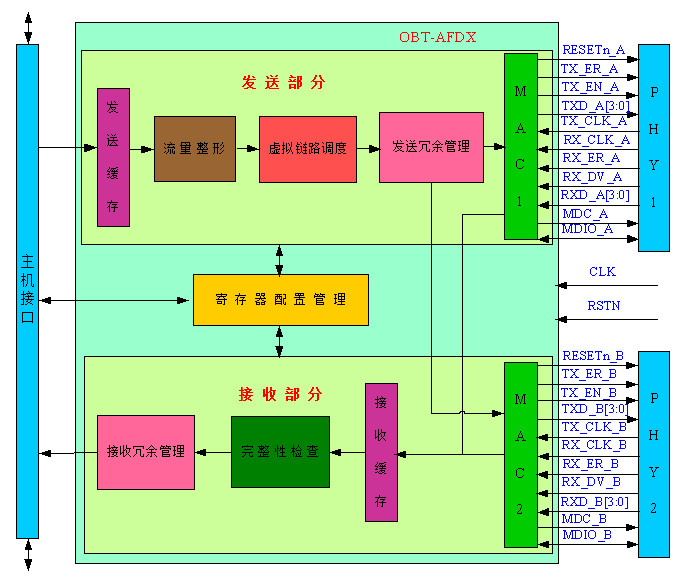

AFDX终端控制器,以下简称OBT-AFDX。OBT-AFDX终端是根据ARINC664第7部分关于AFDX终端的协议规范设计完成的。 AFDX是在IEEE802.3以太网标准框架之内,强化了网络通信的实时性和确定性,用于航空应用的物理连接方式。AFDX 网络体系结构主要由航空电子子系统、端系统和AFDX 互连模块3个部分组成。

端系统是AFDX网络的重要组成部分,它嵌入在航空电子子系统中,将航空电子子系统与AFDX网络连接起来,实现航空电子子系统与AFDX网络发送和接收消息的目的,保证了航空电子子系统与AFDX网络上的其它子系统安全、可靠地进行数据交换。

AFDX网络采用全双工访问,网络中通信节点是预先配置的,不能随机动态增加或删除。同时基于虚拟链路、带宽分配间隙和抖动等概念为每个链路安排了固定的传输带宽和最大传输时延,从源头上避免数据传输过程冲突的产生,从而使AFDX网络具有了实时性和确定性的特性。同时,通过采用双冗余网络,确保了AFDX通讯的可靠性。

♦ 支持ARINC664规范;

♦ 提供2个10/100M的RJ45形式的端口,支持2个端口独立使用或2个端口互为冗余;

♦ 软件实现传输层(UPD)、网络层(IP)协议,硬件实现链路层(Virtual Link)及物理层(PHY)层协议 ;

♦ 高性能的AMBA总线与主机间的数据传输 ;

♦ 支持采样(Sampling)和列队(Queuing)端口;

♦ 支持发送和接收各128条虚拟链路(VL);

OBT-AFDX终端主要实现以下功能:

♦ 配置管理:负责对各个终端的各条虚链路进行参数配置,配置内容包括终端系统的网络ID、设备ID,还包括虚链路中的带宽分配间隙、最大帧长、冗余管理、端口类型、状态等配置参数。

♦ 信息封装:对应用层信息进行UDP、IP和MAC的封装,封装的首部内容根据虚链路的配置参数确定。

♦ 流量整形:为了保证每个VL的带宽分配间隙,调整器对每个虚拟链路的数据帧在发送前按照BAG进行了流量调整。

♦ 虚拟链路调度:当发送ES具有多路VL时,调度器多路复用来自调整器的不同的数据帧,防止数据帧发送的冲突。

♦ 完整性检查:为了保证每条虚链路上信息传送的可靠性,接收终端必须进行完整性检查,在AFDX终端主要依靠对顺序号的检查来实现。

♦ 冗余管理:AFDX网络为了能够保证信息安全发送,防止信息传输过程中的丢失,采用了两个独立的冗余网络进行传输。

图 2‑1 OBT-AFDX功能结构框图

OBT-AFDX结构框图如图2-1所示。各模块功能说明分别如下表2-1所示:

表 2‑1 OBT-AFDX 外部接口信号说明

|

序号 |

信号名称 |

信号方向 |

信号描述 |

|

1 |

CLK |

I |

系统输入时钟 |

|

2 |

RSTN |

I |

外部复位信号,低电平有效 |

|

3 |

AHB( 主机接口) |

I/O |

接AMBA.AHB2.0, 主要是地址线,数据线,读写控制线,数据交互信号线 |

|

4 |

APB( 主机接口) |

I/O |

接AMBA.APB2.0,主要是地址线,数据线,读写控制线,寄存器配置信号线 |

|

5 |

RESETn_A |

O |

通道A复位PHY信号,低电平有效 |

|

6 |

TX_ER_A |

O |

通道A 发送数据错误 |

|

7 |

TX_EN_A |

O |

通道A发送使能,当使能时告诉PHY数据有效 |

|

8 |

TXD_A[3:0] |

O |

通道A发送数据信号 |

|

9 |

TX_CLK_A |

I |

通道A发送单元时钟,PHY提供 |

|

10 |

RX_CLK_A |

I |

通道A接收单元时钟,PHY提供 |

|

11 |

RX_ER_A |

I |

通道A接收错,PHY在当前传输帧提示传输媒质错误 |

|

12 |

RX_DV_A |

I |

通道A接收数据有效,PHY告知MAC数据信号有效 |

|

13 |

RXD_A[3:0] |

I |

通道A接收数据信号 |

|

14 |

MDC_A |

I |

通道A管理数据时钟,MAC提供给PHY |

|

15 |

MDIO_A |

I/O |

通道A管理数据的输入输出,双向数据通道用于MAC和PHY的数据交换 |

|

16 |

RESETn_B |

O |

通道B复位PHY信号,低电平有效 |

|

17 |

TX_ER_B |

O |

通道B 发送数据错误 |

|

18 |

TX_EN_B |

O |

通道B发送使能,当使能时告诉PHY数据有效 |

|

19 |

TXD_B[3:0] |

O |

通道B发送数据信号 |

|

20 |

TX_CLK_B |

I |

通道B发送单元时钟,PHY提供 |

|

21 |

RX_CLK_B |

I |

通道B接收单元时钟,PHY提供 |

|

22 |

RX_ER_B |

I |

通道B接收错,PHY在当前传输帧提示传输媒质错误 |

|

23 |

RX_DV_B |

I |

通道B接收数据有效,PHY告知MAC数据信号有效 |

|

24 |

RXD_B[3:0] |

I |

通道B接收数据信号 |

|

25 |

MDC_B |

I |

通道B管理数据时钟,MAC提供给PHY |

|

26 |

MDIO_B |

I/O |

通道B管理数据的输入输出,双向数据通道用于MAC和PHY的数据交换 |

|

Altera Cyclone III: LE: 43,275 Memory bits: 1,927,936 |

|

Xilinx Virtex5: Slices : 12,497 LUTs : 38,806 Memory bits : 1,927,936 Flip-Flops :22,325 |

| 序号 | 产品型号 | 产品描述 | 备注 |

| 1 | OBTIP-AFDX-T-F | ASIC版本固核(ASIC网表) | / |

| 2 | OBTIP-AFDX-T-V | FPGA版本固核(FPGA网表) | / |

| 3 | OBTIP-AFDX-T-S | 软核(RTL源码) | / |

|

|

|

|

|

资料下载 |