- Part Number Configuration Voltage Clock Rate / Access time Package Temperature SCD#

-

No record

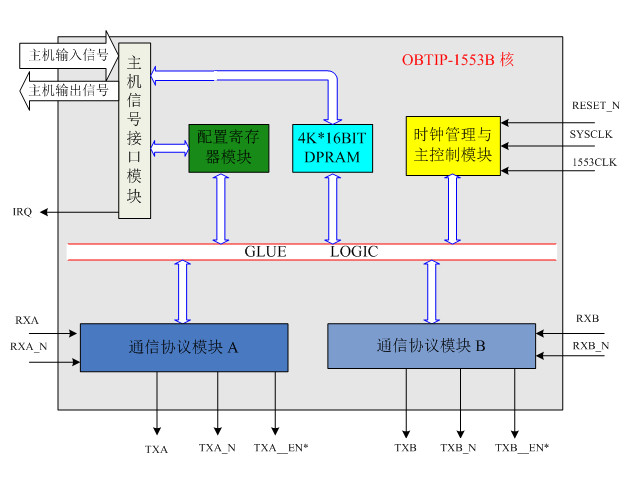

OBT1553B-1M-IP核是依据1553B总线协议(1553A/B Notice2协议)和参考DDC-ACE系列芯片(主要是61580) 设计的IP核。OBT1553B-1M-IP核主要包括通信协议模块A、通信协议模块B、主机信号接口模块、配置寄存器管理模块、存储器管理模块、时钟管理模块和主控制器模块。其中1553通信协议模块部分用差分曼彻斯特编码实现时分命令响应式串行通讯,主要包括A、B通道编码器和解码器;主机信号接口模块实现OBT1553B-1M-IP核与处理器(CPU/DSP/MCU)的接口信号处理;配置寄存器模块主要实现对OBT1553B-1M-IP核的模式、功能和状态等的配置;存储器管理模块为处理器和OBT1553B-1M-IP核之间交互数据的管理方式,主要为4K*16BIT的双口RAM; 时钟管理与主控制模块实现对输入时钟的管理和对OBT1553B-1M-IP核的基本通讯功能的实现与控制,是该IP核的中心控制单元能配置成BC、RT、BM三种类型的控制器。

OBT1553B-1M-IP核主要应用在航空、航天测控网络、兵器及工业控制等技术领域。

►通过硬件逻辑方式完全实现MIL-STD-1553B标准(国军标GJB289A-97标准);

►操作方式、寄存器设置以及存储器布局等方面同BU-61580兼容;

►支持的通讯类型包括:

♦ BC → RT;

♦ RT → BC;

♦ RT → RT;

♦ Broadcast;

♦ Mode code;

►能被配置为BC、RT、BM三种类型的控制器;

►带4K*16Bit 的集成DPRAM,根据需要可进行集成DPRAM的裁减;

►与主机接口模式为同步的AMBA APB2.0信号或通用的异步接口信号;

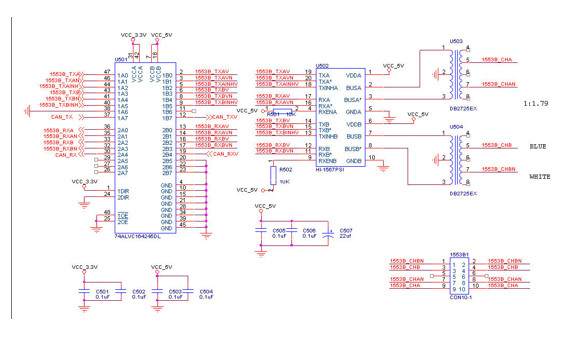

►外部接口支持通用的1553B总线收发器:HI1567、HI1573等

►带A、B双冗余通道;

►BC性能:

♦ 支持A/B区域;

♦ 具有自动重发功能;

♦ 可编程的消息间隔时间;

♦ 帧自动重复发送;

♦ 可编程的超时响应时间;

►RT性能:

♦ 可编程的RT地址,子地址;

♦ 支持单缓冲存储器管理方式;

♦ 支持循环缓冲存储器管理方式;

♦ 支持双缓冲存储器管理方式;

♦ 可编程的非法命令表;

♦ 可编程的方式代码中断表;

♦ 可编程的子地址忙表;

►BM性能:

♦ 能够实时侦听总线上的数据流,可以将所有的数据流记录下来,也可以有选择地进行数据监听;

♦ 支持命令堆栈半满、全满溢出;

♦ 支持数据堆栈半满、全满溢出;

♦ 命令堆栈与数据堆栈独立;

♦ 对每条消息有相应的属性标志;

OBT1553B-1M-IP 核结构框图如图1-1所示。外围接口信号说明如下表1-1所示:

表 1‑1 OBT1553B-1M-IP 核外部接口信号说明

|

序号 |

信号名称 |

信号方向 |

默认状态 |

信号描述 |

|

1 |

RXA |

I |

- |

通道A接收信号 |

|

2 |

RXA_N |

I |

- |

通道A接收信号的反 |

|

3 |

TXA |

O |

0 |

通道A发送信号 |

|

4 |

TXA_N |

O |

0 |

通道A发送信号的反 |

|

5 |

TXA_EN* |

O |

1 |

通道A发送使能信号,主要为外接HI-1567PSI芯片时的使能,低电平有效 |

|

6 |

RXB |

I |

- |

通道B接收信号 |

|

7 |

RXB_N |

I |

- |

通道B接收信号的反 |

|

8 |

TXB |

O |

0 |

通道B发送信号 |

|

9 |

TXB_N |

O |

0 |

通道B发送信号的反 |

|

10 |

TXB_EN* |

O |

1 |

通道B发送使能信号,主要为外接RS485收发器时的使能,低电平有效 |

|

11 |

RESET_N |

I |

- |

外部复位信号低电平有效 |

|

12 |

CLKIN |

I |

16MHZ |

输入时钟 |

|

13 |

IRQN |

O |

1 |

中断信号输出,低电平有效 |

|

14 |

Ext_rtaddr |

I |

- |

RT地址采用内部寄存器配置还是外部输入选择信号,“1”表示RT地址采用外部输入 |

|

15 |

Rt_addr_in[4:0] |

I |

- |

外部输入RT地址 |

|

16 |

Rt_addr_par_in |

I |

- |

外部输入RT地址的奇/偶校验输入,“1”为奇 |

|

17 |

Intel_moto_sel |

I |

- |

异步接口时序Intel/Motorola模式选择信号,1表示Motorola模式 |

|

18 |

Mem_regn |

I |

- |

存贮器与寄存器选择信号,为1选择的是寄存器 |

|

19 |

Addr[11:0] |

I |

- |

外部输入地址信号 |

|

20 |

Data[15:0] |

I/O |

高阻态 |

双向数据信号线 |

|

21 |

Cen |

I |

- |

片选信号线,低电平有效 |

|

22 |

Oen |

I |

- |

输出使能线,低电平有效 |

|

23 |

Wrn |

I |

- |

读写信号线,低电平为写有效 |

|

Altera Cyclone III: LE: 5,152 Memory bits: 65,536 |

|

Xilinx Virtex2: Slices : 2,521 LUTs : 3,566 Memory bits : 65,536 (Block RAMs: 4) Flip-Flops :2,180 |

|

Xilinx Virtex5: Slices : 1347 LUTs : 3,161 Memory bits : 65,536(Block RAMs: 4) Flip-Flops :2,218 |

|

Actel ProASIC3: D-flip-flops(CORE) : 10,328 Memory bits : 65,536(4608-Bit Block: 22) |

|

序号 |

产品型号 | 产品描述 | 备注 |

| 1 | OBTIP-1553B-F | ASIC版本固核(ASIC网表) | / |

| 2 | OBTIP-1553B-V | FPGA版本固核(FPGA网表) | / |

| 3 | OBTIP-1553B-S | 软核(RTL源码) | / |

|

|

资料下载 |