- Part Number Configuration Voltage Clock Rate / Access time Package Temperature SCD#

-

No record

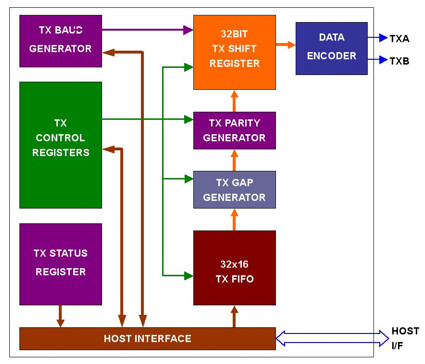

OBT429 IP核中的数据发送模块(简称OBT429-TX)负责接受和处理主机的配置命令,按照ARINC429协议的规定将发送缓存的数据发送到总线网络。

OBT429 IP核中的数据发送模块OBT429-TX具有如下主要特征:

(1) 支持32-bit以及25-bit 的ARINC429数据字长格式;

(2) 不仅支持100Kbps、12.5Kbps、48Kbps、50Kbps等常用的通讯速率,还支持对通讯速率在一定范围内进行任意调节;

(3) 标准配置16x32bit的数据发送缓存FIFO,也支持对发送缓存的容量进行更改;

(4) 支持数据的发送FIFO状态中断(empty、half、full);

(5) 支持奇偶校验(Parity check);

(6) 发送字间间距可调;

OBT429 IP核中的数据发送模块OBT429-TX的结构如图1‑1所示,其主要包含了以下部分:

♦ DATA ENCODER:数据编码器;

♦ BAUD GENERATOR:发送波特率发生器;

♦ TX CONTROL REGISTER:发送控制寄存器;

♦ TX STATUS REGISTER:发送状态寄存器;

♦ 32-BIT TX SHIFTER REGISTER:32位的发送移位寄存器;

♦ TX PARITY GENERATOR:发送奇偶发生器;

♦ TX GAP GENERATOR:发送字间间隙发生器;

♦ TX FIFO:数据发送FIFO(容量为16x32);

♦ HOST INTERFACE:主机接口;

|

序号 |

端口信号 |

方向 |

位宽 |

有效电平 |

信号描述 |

|

1 |

rst |

in |

1 |

L |

片外主复位输入信号 |

|

2 |

clk |

in |

1 |

- |

时钟信号 |

|

3 |

csn |

in |

1 |

L |

片选信号 |

|

4 |

oen |

in |

1 |

L |

读使能信号 |

|

5 |

wrn |

in |

1 |

L |

写使能信号 |

|

8 |

irq |

out |

1 |

H |

中断信号 |

|

9 |

addr |

in |

3 |

- |

地址总线信号 |

|

10 |

data |

inout |

15 |

- |

数据总线信号 |

|

11 |

txa |

out |

1 |

- |

数据发送信号正端 |

|

12 |

txb |

out |

1 |

- |

数据发送信号负端 |

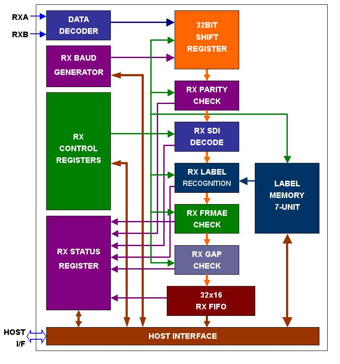

OBT429 IP核中的数据接收模块(简称OBT429-RX)负责接受和处理主机的配置命令,按照ARINC429协议的规定从总线网络上接收数据并将其存入接收缓存。

OBT429 IP核中的数据接收模块OBT429-RX具有如下主要特征:

(1) 支持32-bit以及25-bit 的ARINC429数据字长格式;

(2) 不仅支持100Kbps、12.5Kbps、48Kbps、50Kbps等常用的通讯速率,还支持对通讯速率在一定范围内进行任意调节;

(3) 标准配置16x32bit的数据接收缓存FIFO,也支持对接收缓存的容量进行更改;

(4) 支持数据的接收FIFO状态中断(empty、half、full);

(5) 支持硬件方式的SDI解码(SDI decode);

(6) 支持硬件方式的7个LABEL识别(Label recognition);

(7) 支持硬件方式的奇偶校验(Parity check);

ARINC429的数据接收模块的结构如图14‑1所示,其主要包含了以下部分:

♦ DATA DECODER:数据解码器;

♦ BAUD GENERATOR:接收波特率发生器;

♦ RX CONTROL REGISTER:接收控制寄存器;

♦ RX STATUS REGISTER:接收状态寄存器;

♦ 32-BIT SHIFTER REGISTER:32位的移位寄存器;

♦ RX PARITY CHECK:接收奇偶校验;

♦ RX SDI CHECK:接收SDI校验;

♦ RX LABEL CHECK:接收LABEL校验;

♦ RX FRAME CHECK:接收字连续性校验;

♦ RX GAP CHECK:接收字间间隙校验;

♦ LABEL MEMORY:LABEL存储器(容量为7);

♦ RX FIFO:数据接收FIFO(容量为16x32);

♦ HOST INTERFACE:主机接口;

|

序号 |

端口信号 |

方向 |

位宽 |

有效电平 |

信号描述 |

|

1 |

rst |

in |

1 |

L |

片外主复位输入信号 |

|

2 |

clk |

in |

1 |

- |

时钟信号 |

|

3 |

csn |

in |

1 |

L |

片选信号 |

|

4 |

oen |

in |

1 |

L |

读使能信号 |

|

5 |

wrn |

in |

1 |

L |

写使能信号 |

|

8 |

irq |

out |

1 |

H |

中断信号 |

|

9 |

addr |

in |

3 |

- |

地址总线信号 |

|

10 |

data |

inout |

15 |

- |

数据总线信号 |

|

11 |

rxa |

in |

1 |

- |

数据接收信号正端 |

|

12 |

rxb |

in |

1 |

- |

数据接收信号负端 |

| 序号 | 产品型号 | 产品描述 | 备注 |

| 1 | OBTIP-429-F | ASIC版本固核(ASIC网表) | / |

| 2 | OBTIP-429-V | FPGA版本固核(FPGA网表) | / |

| 3 | OBTIP-429-S | 软核(RTL源码) | / |

OBT429-IP核用户手册V2.1.pdf OBT429-IP核用户手册V2.1.pdf

|

资料下载 |