- Part Number Configuration Voltage Clock Rate / Access time Package Temperature SCD#

-

No record

OBT-CAN实现了CAN 2.0B协议,支持BasicCAN和PeliCAN模式,这两种模式可以通过时钟分频寄存器选择。在BasicCAN和PeliCAN两种模式下寄存器的映射有所不同。

OBT-CAN控制器共有32个寄存器,地址分别为0-31。在CPU看来,CAN控制器相当于存储器地址映射的I/O设备,CPU对CAN控制器的所有操作都是通过访问寄存器实现的。

OBT-CAN控制器主要特征

► PCA82C200 模式(即默认的BasicCAN 模式)

► 扩展的接收缓冲器(64字节先进先出FIFO)

► 和CAN2.0B协议兼容

► 同时支持11位和29位标识符

► 位速率可达1Mbits/s

► PeliCAN模式扩展功能

♦ 可读/写访问的错误计数器

♦ 可编程的错误报警限制

♦ 最近一次错误代码寄存器

♦ 对每一个CAN 总线错误的中断

♦ 具体控制位控制的仲裁丢失中断

♦ 单次发送(无重发)

♦ 只听模式(无确认、无活动的出错标志)

♦ 支持热插拔(软件位速率检测)

♦ 验收过滤器扩展(4字节代码,4字节屏蔽)

♦ 自身信息接收(自接收请求)

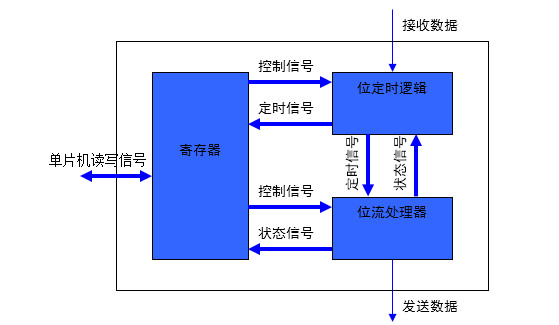

CAN控制器主要由寄存器、位定时逻辑和位流处理器3个模块组成,如图1‑1所示。

CAN寄存器是与CPU连接的模块,CPU对CAN控制器的所有操作都是通过寄存器进行的。

位定时逻辑实现的主要功能是检测CAN总线输入信号和来自位流处理器的CAN总线输出信号,输出采样点、采样位、发送点和同步信号等位定时信息。

位流处理器实现的主要功能是输入来自寄存器的寄存器信息和来自位定时逻辑的采样点、采样位、发送点和同步信号等位定时信息,对采样位的位流进行处理,并输出状态信息和CAN总线输出信号。

|

序号 |

信号名称 |

信号方向 |

默认状态 |

信号描述 |

|

1 |

rst_n |

I |

- |

外部复位信号高电平有效 |

|

2 |

ale |

I |

- |

ALE 输入信号 |

|

3 |

rd_n |

I |

- |

微控制器的/RD信号(Intel模式)或E使能信号(Motorola模式) |

|

4 |

wr_n |

I |

- |

微控制器的/wr信号(Intel模式)或RD/(/WR)信号(Motorola模式) |

|

5 |

port_io |

I/O |

- |

多路地址/数据总线 |

|

6 |

cs_n |

I |

- |

片选信号,低电平有效 |

|

7 |

clk_i |

I |

- |

时钟信号输入 |

|

8 |

rx_i |

I |

- |

接收数据信号端 |

|

9 |

tx_o |

O |

- |

发送数据信号端 |

|

10 |

Mode |

I |

- |

模式选择信号 |

|

11 |

irq_n |

O |

- |

中断请求信号 |

|

12 |

clkout_o |

O |

- |

CAN分频后时钟信号输出 |

|

Altera Cyclone III: LE: 24,593 Memory bits: 5,248 |

|

Xilinx Virtex2: Slices : 3,500 LUTs : 6,109 Memory bits : 5,248 Flip-Flops :1,239 |

|

Xilinx Virtex5: Slices : 1,346 LUTs : 3,410 Memory bits : 5,248 Flip-Flops :1,260 |

|

Actel ProASIC3: D-flip-flops(CORE) : 27,308

|

| 序号 | 产品型号 | 产品描述 | 备注 |

| 1 | OBTIP-CAN-F | ASIC版本固核(ASIC网表) | / |

| 2 | OBTIP-CAN-V | FPGA版本固核(FPGA网表) | / |

| 3 | OBTIP-CAN-S | 软核(RTL源码) | / |

OBTCAN-IP核用户手册(V2.1).pdf OBTCAN-IP核用户手册(V2.1).pdf

|

资料下载 |